ENP2505_DataSheet.pdf

|IXP1200 Dummy's Guide.pdf|

|Meetings

|Environment

|Hardware

|Setup

|SDK

|Run

|Run2

|Programming

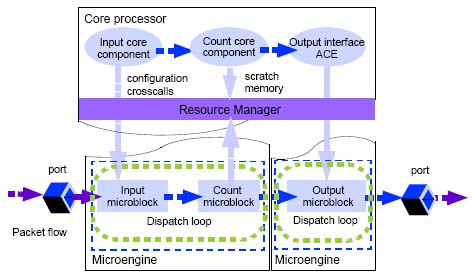

|ACE

|Experiences

|Links

|NSC WCR|

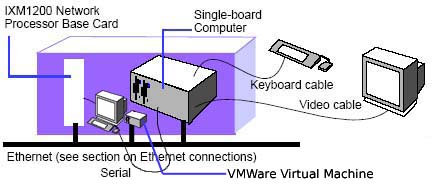

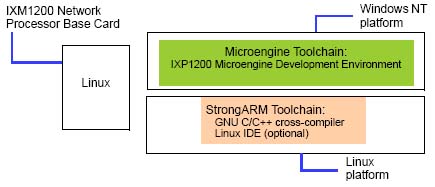

Software Configuration

Software Configuration [Top]

[Top]

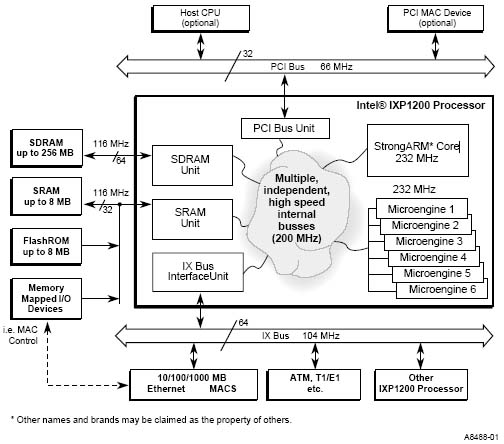

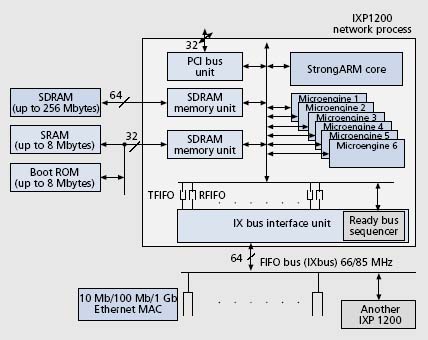

Block Notes

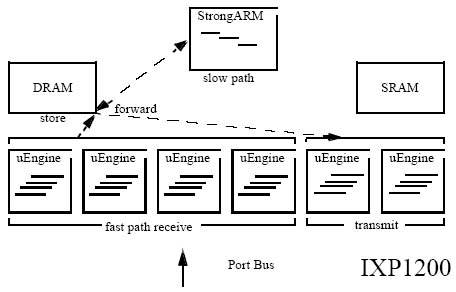

Block Notes| Internal Buses 200 Mhz |

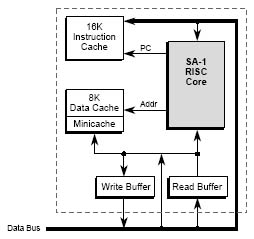

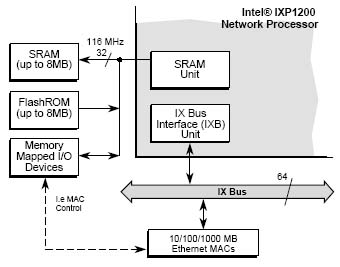

StrongARM (ARM = Advanced Reduced Instruction Set Computer (RISC) Machine) | 232 MHz |

| 6 Microengines (4 non-preemptive Threads in round-robin order for each, RISC) | 232 MHz | |

| SDRAM (256MB, 64-bit data path) | 116 MHz | |

| SRAM (8MB, 32-bit data path) | 116 MHz | |

| IX Bus Interface (RFIFO, TFIFO) | 104 MHz | |

| PCI Bus | 66 MHz |

| Memory Interface | Minimum Addressable Unit (bytes) | Size (bytes) | Approx. Unloaded Latency (clks) | Sepcial Operations |

|---|---|---|---|---|

| Scratchpad | 4 | 4K (on chip) | 12 - 14 | Atomic increment, bit test-and-set, bit test-and-clear |

| SRAM | 4 | 8M (addressable) | 16 - 20 | Content Addressable Memory (CAM) lock, bit tes-and-set, bit test-and-clear, push-pop queues |

| SDRAM | 8 | 256M (addressable) | 33 - 40 | Direct path to and from the FBI which allows data to be moved between the two without first going through one of the processors. |

Data can be moved simultaneously

Data can be moved simultaneously

Citing from IEEE Journal

Citing from IEEE Journal

StrongARM Core Internal Connections

StrongARM Core Internal Connections| Unit | Resource |

|---|---|

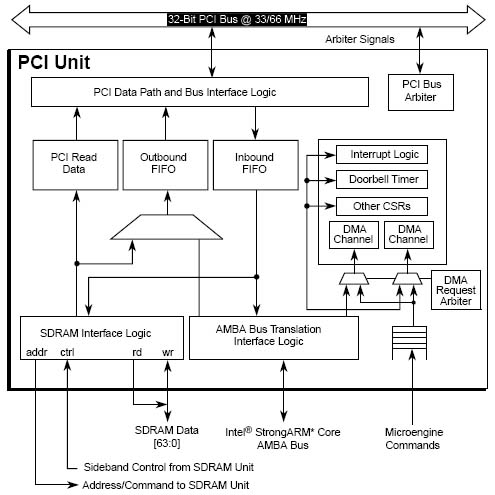

| PCI Unit |

Full access to the PCI Bus, including all PCI bus transactions. Full access to PCI Unit registers. Separate, shared 32-bit bus between the StrongARM core (ATU) data bus and the PCI Unit. |

| SDRAM Unit | Full access to SDRAM. |

| SRAM Unit | Full access to SRAM, including Flash and other devices hooked up to the SRAM Bus. |

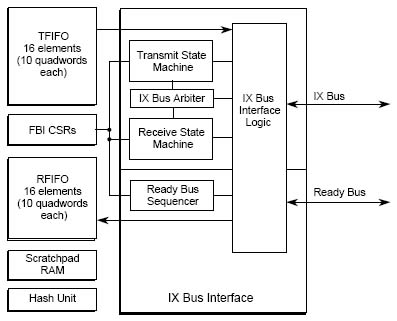

| IX Bus Unit |

Access to Control and Status registers within the IX Bus Unit. Access to Scratchpad RAM within the IX Bus Unit. No access to the Receive or Transmit FIFOs or the IX data bus. |

| Microengines |

Access to Microengines' Program Control Store to program the Microengines. Access to Control and Status Registers, including PC (Program Counter). No access to Microengine Transfer Registers. |

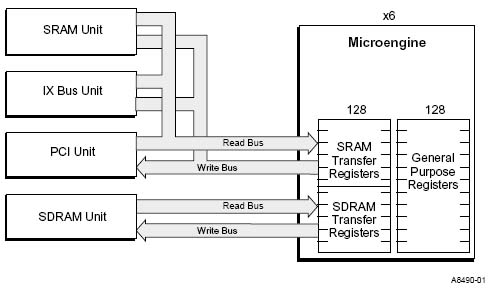

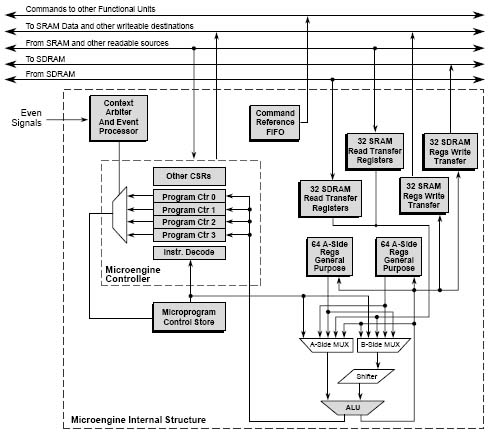

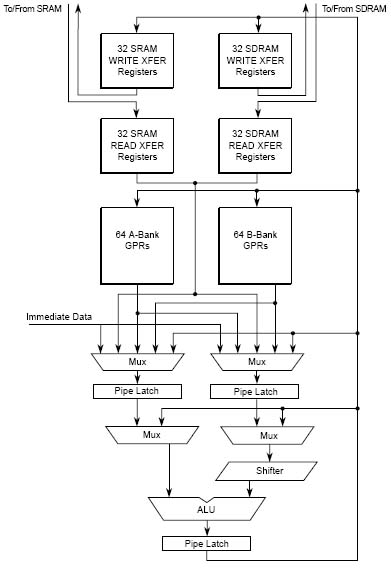

Microengines have 3 different types of registers:

Microengines have 3 different types of registers:| Register Type | Explanation |

|---|---|

| General purpose | Each microengine has 128, 32-bit general purpose registers (GPRs), allocated into two banks of 64 registers (A and B banks). In thread-local mode, each thread accesses a unique set of 32 GPRs, or 16 A bank GPRs and 16 B GPRs. In absolute mode, GPRs registers are accessible by any thread. Absolute registers are useful for inter-thread communication within a microengine. |

| SRAM transfer | Each Microengine has 64 SRAM transfer registers divided equally into read-only and write-only. SRAM transfer registers are used to read from and write to all functional units on the IXP12xx except for the SDRAM unit. When data is read from other functional units, it its placed in SRAM transfer registers, and when microengine code writes data to these units, it must firest be placed in transfer registers. |

| SDRAM transfer | Each microengine has 64 SDRAM transfer registers divided equally into read-only and write-only. SDRAM transfer registers are used exclusively for communication between the microengines and the SDRAM unit. |

| Unit | Resource |

|---|---|

| StrongARM Core |

The Microengines may interrupt the StrongARM core. The StrongARM core can read aregister to determine which Microengine generated the interrupt. No other access to StrongARM Core. |

| PCI Unit | No access to the PCI Bus. Access only to the Control and Status Registers for the two DMA Controllers in the PCI Unit. By programming these registers, the Microengines may initiate DMA transfers between a block of SDRAM memory and a PCI device. |

| SDRAM Unit | Full access to SDRAM. |

| SRAM Unit | Full access to SRAM, including Flash and other devices hooked up to the SRAM Bus. |

| IX Bus Unit | Full access to the IX Bus Unit, including the Scratchpad RAM, Hardware Hashing Unit, Receive and Transmit FIFOs, Ready Bus, and Control and Status Registers. |

| Microengines |

Each Microengine has access to its Program Control Store so it can execute instructions. The Microengines do not have read or write access to the Control Store (they cannot read or write their own Control Store, only the StrongARM core can do that). Inter-thread signalling between Microengine threads is provided. Each Microengine is self-contained, so one Microengine cannot access the Control Store, or Registers of another Microengine. |

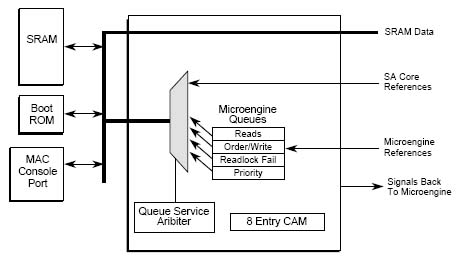

SRAM Unit Internal Connections

SRAM Unit Internal Connections| Unit | Resource |

|---|---|

| StrongARM Core | Full access. |

| PCI Unit | No connection between the SRAM Unit and the PCI Unit. |

| SDRAM Unit | No connection between the SRAM Unit and the SDRAM Unit. |

| IX Bus Unit | No connection between the SRAM Unit and the IX Bus Unit. |

| Microengines | Full access. |

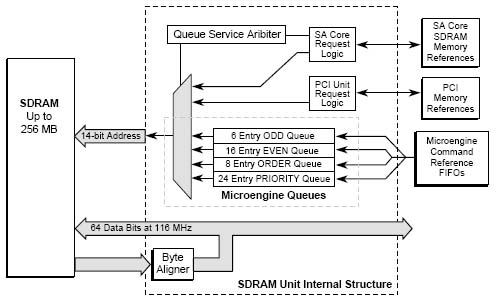

SDRAM Unit Internal Connections

SDRAM Unit Internal Connections| Unit | Resource |

|---|---|

| StrongARM Core | Full access. |

| PCI Unit |

There is a separate, and unshared 32-bit bus connecting the SDRAM Unit and the PCI Bus Unit. This allows devices on the PCI Bus better access to data buffers within the SDRAM Unit. The two DMA Controllers in the PCI Unit have access to SDRAM data. |

| SRAM Unit | No connection between the SRAM Unit and the SRAM Unit. |

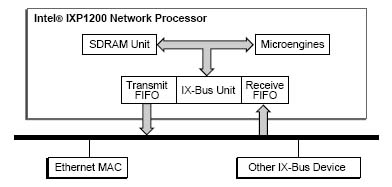

| IX Bus Unit | There is a 32-bit bus connecting the SDRAM Unit and the IX-Bus Unit’s Receive and Transmit FIFOs. |

| Microengines | Full access. |

PCI Unit Internal Connections

PCI Unit Internal Connections| Unit | Resource |

|---|---|

| StrongARM Core | Full access. The StrongARM core can access any devices on the PCI Bus. The StrongARM core can program any of the PCI Unit’s Control and Status Registers. |

| SDRAM Unit |

Unshared, direct 32-bit bus connecting SDRAM Unit and the PCI Unit. Devices on the PCI Bus have access to SDRAM. DMA Controllers within the PCI Unit can transfer data between SDRAM and devices on the PCI Bus. |

| SRAM Unit |

No connection between the SRAM Unit and the PCI Unit. Devices on the PCI Bus cannot access SRAM. DMA Controllers within the PCI Unit cannot access SRAM. |

| IX Bus Unit |

No connection between the IX Bus Unit and the PCI Unit. Data that needs to be transferred between the IX Bus (Transmit and Receive FIFOs) and the PCI Bus must be transferred by the Microengines (by way of their Transfer Registers). |

| Microengines |

The Microengines can only access the Control and Status Registers for the DMA Controllers within the IX Bus Unit. No other access. The Microengines cannot access devices on the PCI Bus (and vice versa). |

IX Bus data flow

IX Bus data flow PCI Unit Internal Connections

PCI Unit Internal Connections| Unit | Resource |

|---|---|

| StrongARM Core |

Limited Access. The StrongARM core can access the Scratchpad RAM within the IX Bus Unit, as well as a number of Control and Status Registers within the IX Bus Unit. The StrongARM Core cannot access the Receive and Transmit FIFOs within the IX Bus Unit. The StrongARM Core can program the Ready Bus Controller within the IX Bus Unit. |

| SDRAM Unit | Two direct, unshared, independent busses connect the SDRAM Unit with the IX Bus Unit. The SDRAM read bus is connected to the Receive FIFO, while the write bus is connected to the Transmit FIFO. |

| SRAM Unit | No connection between the SRAM Unit and the IX Bus Unit’s FIFOs. Data that needs to be transferred between the IX Bus (Transmit and Receive FIFOs) and SRAM must be transferred by the Microengines (by way of their Transfer Registers). |

| PCI Unit |

No connection between the IX Bus Unit and the PCI Unit. Data that needs to be transferred between the IX Bus (Transmit and Receive FIFOs) and the PCI Bus must be transferred by the Microengines (by way of their Transfer Registers). |

| Microengines | Full Access, including access to the Scratchpad RAM, the Hashing Unit, programming the Ready Bus Controller, the Receive and Transmit FIFOs, and all Control and Status Registers. |

| Mount Point | Filesystem Type | Size (MB) | Additional Size Options |

|---|---|---|---|

| /boot | ext2 | 128 | Fixed size |

| swap | 512 | Fixed size | |

| / | ext2 | Fill to maximum allowable size |

default=1 title RedHat Linux (2.4.7) root (hd0, 0) kernel vmlinuz-2.4.7-10 ro root=/dev/hda0 initrd /initrd-2.4.7-10.img title RedHat Linux (2.4.17) root (hd0, 0) kernel vmlinuz-2.4.17-10 ro root=/dev/hda0 initrd /initrd-2.4.7-10.img設定tftp開機service。vi /etc/xinetd.d/tftp

service tftp

{

socket_type = dgram

protocol = udp

wait = wait

user = nobody

log_on_success += USERID

log_on_failure += USERID

server = /usr/sbin/in.tftpd

server_args = /tftpboot -l

disabled = no

}

新的kernel沒有支援intel以外的網卡,也沒有iptables,所以要重新將網卡和iptables的module安裝起來需要重新編譯核心:

cd /usr/src/linux-2.4.17 make menuconfig (or make xconfig) (Network devices -> Realtek RTL8139 or others...) (Networking options -> Network packet filtering (replaces ipchains)) (Networking options -> IP: Netfilter Configuration -> IP tables support...) (Networking options -> IP: Netfilter Configuration -> Connection tracking (required for masq/NAT)) (Networking options -> IP: Netfilter Configuration -> Full NAT -> MASQUERADE) make dep make clean make bzImage make modules make modules_install make install (筆記註:龜毛的話再改一次/etc/grub.conf。)reboot. Install the Intel IXA SDK

# IXA SDK path settings if ! echo $PATH | /bin/grep -q "/usr/local/armbe/bin" ; then PATH="$PATH:/usr/local/armbe/bin" fi if ! echo $PATH | /bin/grep -q "/opt/ixasdk/bin" ; then PATH="$PATH:/opt/ixasdk/bin" fi IXROOT="/opt/ixasdk" CONFIG="ARM_BE" export PATH USER LOGNAME MAIL HOSTNAME HISTSIZE INPUTRC IXROOT CONFIGInstalling IXA SDK on the Windows Development Workstation

echo 1 > /proc/sys/net/ipv4/ip_forward // 開啟ip_forward

(或是修改/etc/sysctl.conf設定variable net.ipv4.ip_forward = 1)

/sbin/iptables -t nat -A POSTROUTING -o vmnet8 -s 192.168.0.2 -j MASQUERADE

ENP Configuration

cd /opt/ixasdk/enp2505/src/linuxIXAedu make menuconfig Select "System and processor types" Under "IXP Board type" select ENP-2505 Select "Save and exit" make dep; make clean; make zImageThis procedure will copy the zImage kernel into /tftpboot for the PCI download scripts. Applying the IXA SDK patch

cd /opt tar -zcvf ixasdk.tgz ixasdk cp /mnt/cdrom/ENP_UPDATES_FOR_IXA_SDK/enp_changes_ixa_sdk.path /opt cd /opt/ixasdk cat ../enp_changes_ixa_sdk.patch | patch -plRebuilding the pciDg dirver module

ARM-TOOLS = /usr/local/armbe/bin/armv4b-unknown-linux- ARM-KERNEL-INCLUDES = $(PWD)/../linuxIXAedu/include X86-KERNEL-INCLUDES =或是ln -s /opt/ixasdk/enp-2505/src/linuxIXAedu /opt/ixasdk/enp-2505/src/linux make clean; make Rebuilding the SDK

cd /opt/ixasdk/src/microace make clean; makeENP2505/6 Specific Configuration

cd /opt/ixasdk/enp-2505/bootixp ./bootixpVerifying ENP-2505/6 Driver operation

On ENP: Module Size Used by pciDgNet-arm 2668 1 pciDg-arm 7544 0 [pciDgNet-arm] On Linux: Module Size Used by pciDgNet 1920 1 pciDg 5568 0 [pciDgNet]ping 192.168.0.4(Linux) 192.168.0.2(ENP)

echo 1 > /proc/sys/net/ipv4/ipforward 編輯/etc/sysctl.conf variable net.ipv4.ip_forward = 1 -----VMWare Windows----- iptables -t nat -A POSTROUTING -o vmnet8 -s 192.168.0.2 -j MASQUERADE ------------------------[Top] SDK

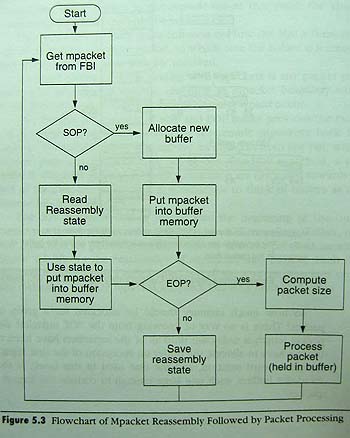

Microengine C RFC1812 Example Data Flow

Microengine C RFC1812 Example Data Flow Flowchart of Mpacket Reassembly Followed by Packet Processing

Flowchart of Mpacket Reassembly Followed by Packet Processing [Top]

[Top]

$IXROOT = /opt/ixasdk $CONFIG = ARM_BE

cd $IXROOT/src/microace/aces/tutorial1/ucbuild

make -f Makefile.winftp to linux:

ftp> cd /opt/ixasdk/bin/arm-be ftp> mput *.uof

cd $IXROOT/src/microace/aces/tutorial1/count_ace1

(make clean;) make

cd $IXROOT/src/microace/projects/Count_8_1Edit ixsys_count_8_1.config.

(make clean;) make(This will export ixsys_count_8_1.config to the directory $IXROOT/bin/arm_be.)

cd /nfs/ixasdk/bin/arm-be

./ixstart ixsys_count_8_1.config(If needed, Start Debugging at workbench side.)

$IXROOT = /opt/ixasdk $CONFIG = ARM_BE

cd $IXROOT/src/microace/aces/tutorial1/ucbuild

make -f Makefile.winftp to linux:

ftp> cd /opt/ixasdk/bin/arm-be ftp> mput *.uof

cd $IXROOT/src/microace/apps/l3config

(make clean;) make

cd $IXROOT/src/microace/aces/l3forward_aceEdit ixsys.config-l3fwdr.

(make clean;) make(This will export ixsys.config-l3fwdr to the directory $IXROOT/bin/arm_be.)

cd /nfs/ixasdk/bin/arm-be

./ixstart ixsys.config-l3fwdr

| Term | Bits |

|---|---|

| Byte | 8 |

| Word | 16 |

| Longword | 32 |

| Quadword | 64 |

Register Naming Conventions

Register Naming Conventions| Register Name Form | Meaning |

|---|---|

| reg_name | Context-relative GPR |

| @reg_name | Absolute GPR |

| $reg_name | Context-relative SRAM XFER register |

| @$reg_name | Absolute SRAM XFER register |

| $$reg_name | Context-relative SDRAM XFER register |

| @$$reg_name | Absolute SDRAM XFER register |

| Feature | Directive |

|---|---|

| Assembler Loops | #for #repeat #while #endloop |

| Assembler Macros | #macro #endm |

| Conditional Assembly | #ifdef #ifndef #if #else #elif #endif |

| Error Reporting | #error #warning |

| Export Function | .export_func |

| File Inclusion | #include |

| Function Table | .func_table |

| Import Variable | .import_var |

| Linker Directives | .image_name .entry .page .thread_type .ucode_size |

| Local Regions | .local .endlocal |

| Manual Register Specification | .areg .breg .$reg .$$reg |

| Operand Synonym | .operand_synonym |

| Structured Assembly | .if .elif .else .endif .repeat .until .while .endw .break .continue |

| Subroutine Definition | .subroutine .endsub |

| Token Replacement | #define #undef #define_eval |

| Transfer Order | .xfer_order .xfer_order_rd .xfer_order_wr |

| Segment | .segment |

| Virtual Set | .set |

| Instruction | Description |

|---|---|

| Arithmetic, Rotate, and Shift Instructions | |

| ALU | Perform an ALU operation. |

| ALU_SHF | Perform an ALU and shift operation. |

| DBL_SHF | Concatenate two longwords, shift the result, and save a longword. |

| Branch and Jump Instructions | |

| BR, BR=0, BR!=0, BR>0, BR>=0, BR<0, BR<=0, BR=cout, BR!=cout |

Branch on condition code. |

| BR_BSET, BR_BCLR | Branch on bit set or bit clear. |

| BR=BYTE, BR!=BYTE | Branch on byte equal. |

| BR=CTX, BR!=CTX | Branch on current context. |

| BR_INP_STATE | Branch on event state (e.g., SRAM done). |

| BR_!SIGNAL | Branch if signal deasserted. |

| JUMP | Jump to label. |

| RTN | Return from a branch or a jump. |

| Reference Instructions | |

| CSR | CSR reference. |

| FAST_WR | Write immediate data to the thd_ done CSRs. |

| LOCAL_CSR_RD, LOCAL_CSR_WR | Read and write CSRs. |

| R_FIFO_RD | Read the receive FIFO. |

| PCI_DMA | Issue a request to the PCI Unit. |

| SCRATCH | Scratchpad reference. |

| SDRAM | SDRAM reference. |

| SDRAM_CRC | SDRAM CRC reference. (IXP1240 and IXP1250 only) |

| SRAM | SRAM reference. |

| T_FIFO_WR | Write to the transmit FIFO. |

| Local Register Instructions | |

| FIND_BSET, FIND_BSET_WITH_MASK | Determine position number of first bit set in an arbitrary 16-bit field of a register. |

| IMMED | Load immediate word and sign extend or zero fill with shift. |

| IMMED_BO, IMMED_B1, IMMED_B2, IMMED_B3 | Load immediate byte to a field. |

| IMMED_WO, IMMED_W1 | Load immediate word to a field. |

| LD_FIELD, LD_FIELD_W_CLR | Load byte(s) into specified field(s). |

| LOAD_ADDR | Load instruction address. |

| LOAD_BSET_RESULT1, LOAD_BSET_RESULT2 | Load the result of a find_bset or find_bset_with_mask instruction. |

| Miscellaneous Instructions | |

| CTX_ARB | Perform context swap and wake on event. |

| NOP | Perform no operation. |

| HASH1_48, HASH2_48, HASH3_48 | Perform 48-bit hash. |

| HASH1_64, HASH2_64, HASH3_64 | Perform 64-bit hash. |

| Date | Experiences |

|---|---|

| 2004/03/01 | Y. K. Chuang: "我們做資訊的,不可能把所有東西都搞懂之後才動工... 跳進去發現問題再出來,直接實作發現問題之後再來找答案會比較實在。" |

| 2004/03/02 | 蘇文鈺: "學習任何一種組語最先要做同時也最重要的是把硬體架構搞懂。" |

| 2004/03/09 | jasonmel: 多看圖案,看不懂再看文字,可以大幅提升閱讀速度也大幅減少看文字的發呆次數。另外邊看邊做筆記效果也比較好。 |

| 2004/07/04 | jasonmel: 實際操作一次勝過光看文字十遍。 |